指令周期

基本概念

冯诺依曼机,即存储程序式计算机,在程序运行前需要把程序和数据放入内存

执行程序流程:

把程序首地址送入PC

从内存cache中取指,执行,并形成下一条指令的地址

自动执行直到程序的最后一条指令

也就是“取指-执行”的循环

指令周期是指“取指令、分析指令并执行指令所需的总时间”

由于各种指令功能不同,所以各种指令的周期长度可能不同

三个周期:

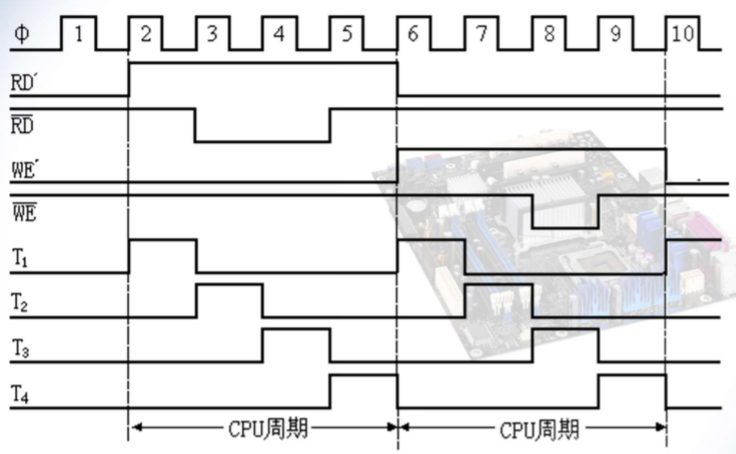

时钟周期,处理操作的基本单位,也称为节拍脉冲或T周期

CPU周期,也称机器周期,指从内存中读取一个指令字的最短时间,通常包含若干个时钟周期

指令周期通常包含若干个CPU周期

RR型指令举例 - MOV指令的指令周期

不同的CPU结构会影响指令周期

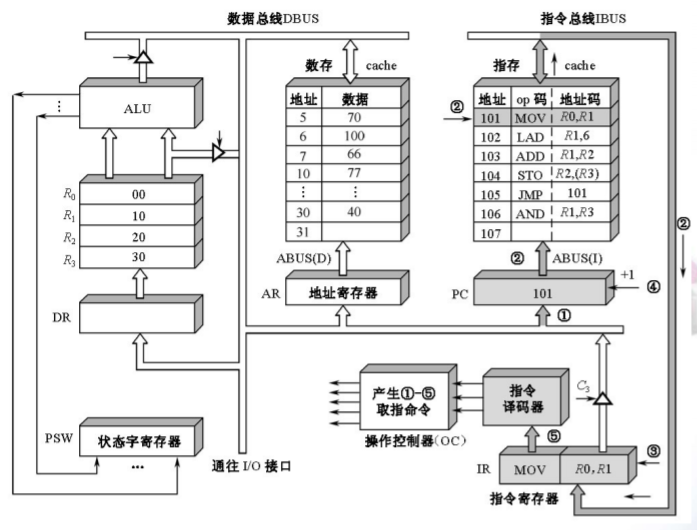

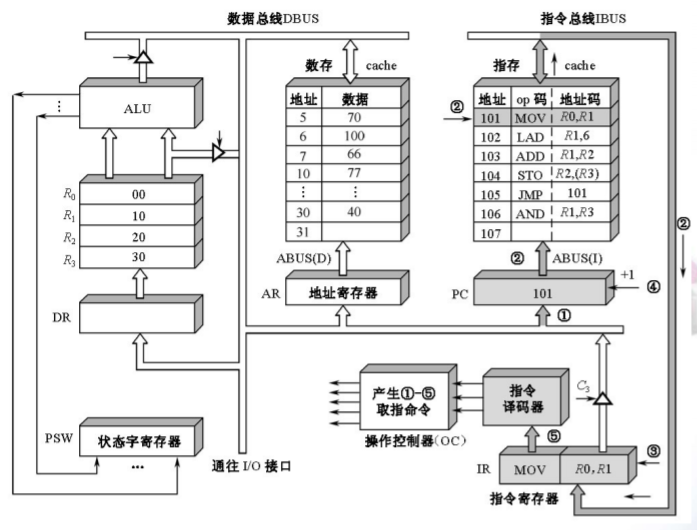

本例中使用的CPU模型如下

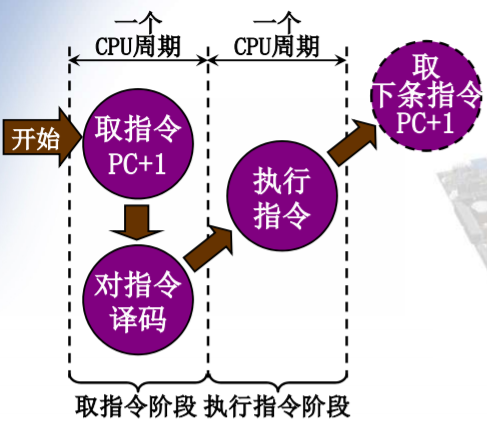

MOV的指令周期如下:

MOV指令是RR型指令,只有取指需要访存,所以只要两个CPU周期即可。一个CPU周期取指(回忆-CPU周期是从内存取出一个指令字的最短时间),另一个周期执行。执行不需要访存,寄存器之间的操作非常迅速,所以会在一个CPU周期内完成。而指令周期的最小单位是CPU周期,所以MOV需要两个完整的CPU周期

取指周期图示:

取指阶段:

根据PC从内存中取出指令

指令译码或测试(逻辑电路而非时序电路,不花费时间)

PC+1

对应的操作:

PC -> ABUS(I)

IBUS ->IR

PC + 1

RS型指令举例 - LAD指令的指令周期

LAD指令为RS型指令,需要三个CPU周期

所有指令的取指阶段都是一样的,取指花费一个CPU周期

把指令中的地址字段交给地址寄存器AR。此过程不访存,花费不到一个CPU周期,但是数据通过DBUS到达AR,占用了总线,所以按照一个CPU周期计算

从内存中取出数据到DR(回忆-DR为数据缓冲寄存器,几乎一切数据都要经过DR再到目的地),通过DBUS,需要一个完整的CPU周期

DR把数据交给通用寄存器R0,不访存,不使用总线,花费不到一个CPU周期,可以和上面的操作一起完成

各指令的指令周期小结

判断一个过程是否占用一整个CPU周期,判断依据1:有没有访存,因为每次访存会消耗一个CPU周期;判断依据2:有没有多个操作占用同一条总线。如果有则把两个操作放置到两个CPU周期中。无总线冲突且不访存的操作可以和前面的访存操作合并在一个CPU周期中

取指操作中在把指令放入指令寄存器/指令译码器之后要等待下一个CPU周期来执行指令

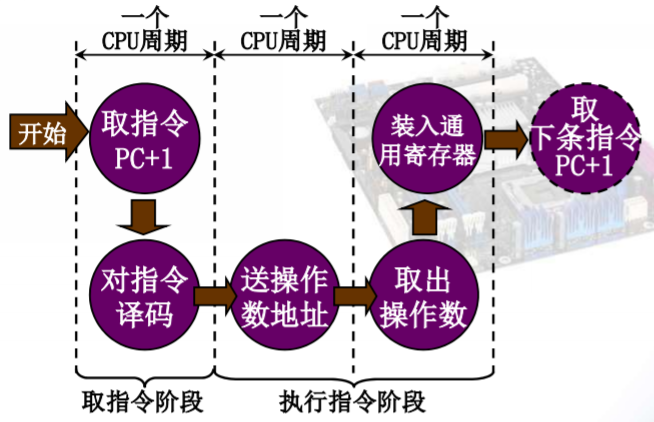

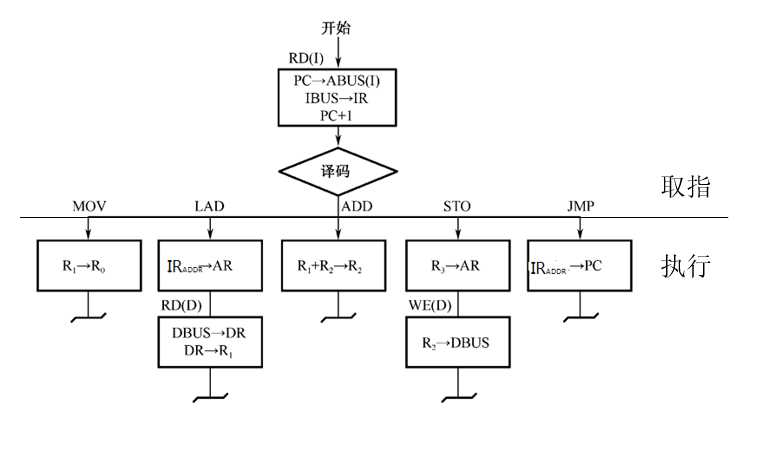

用方框图语言表示的指令周期

方框:按CPU周期(方框内内容——数据通路操作或控制操作)

菱形框:判别或测试

流线:表示指令的运行顺序

~:公操作

如下图为例: 第一个方框为取值周期,需要一个CPU周期。菱形框译码,判别是下面五个指令中的哪个。其中LAD和STO指令为RS型指令,需要两个CPU周期进行执行。

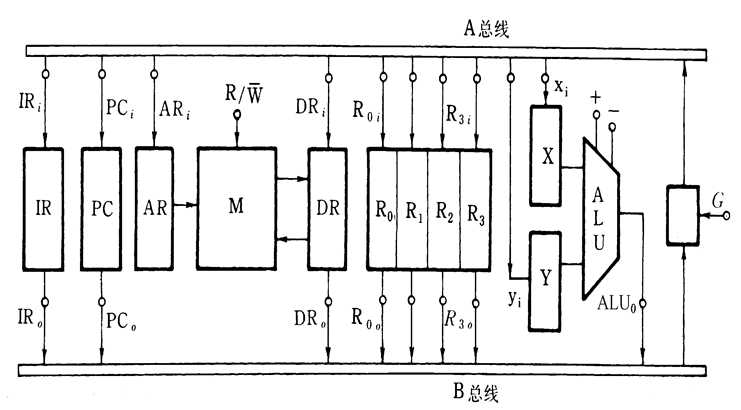

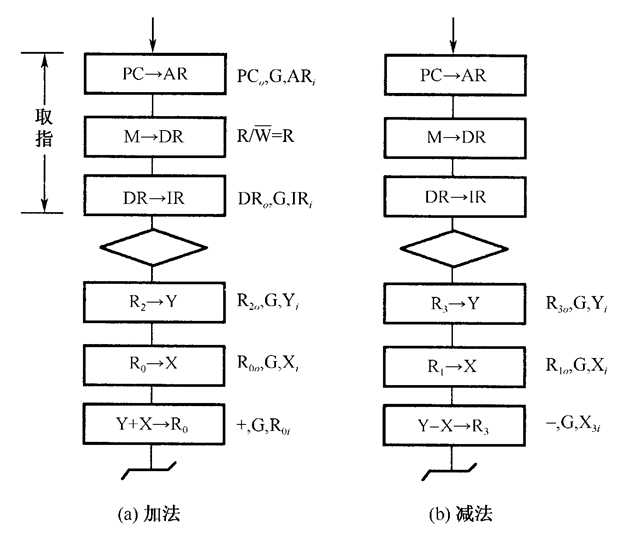

双总线结构机器的数据通路图:

有A、B总线,通过微操作信号(如 𝑃𝐶𝑖,𝐼𝑅𝑖,𝐼𝑅0 等),中间的部件与总线相连形成数据通路,微操作信号为高电平表示该部件与对应总线相连(如𝐼𝑅𝑖为1表示IR部件和A总线互通),最右边的G的电平为1表示AB总线相连。

指令执行过程的微操作信号(每个方框右边)如下:

时序产生器

如何识别二进制码是指令还是数据?如果是取指阶段读出的那就是指令,如果是执行阶段读出的那就是数据。被送往指令寄存器的是指令,被送往运算器的是数据

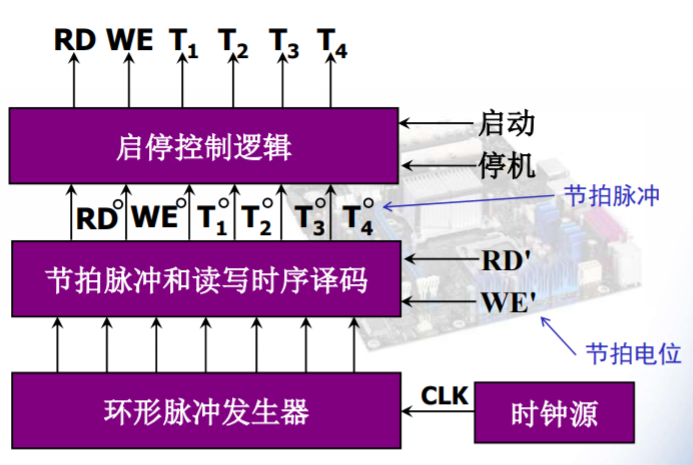

时序信号产生器的组成

时钟源

环形脉冲发生器

节拍脉冲和读写时序的译码

启停控制逻辑

结构框图:

输出信号:

启停控制逻辑的控制方式

同步控制方式

任何情况下各指令执行时所需的机器周期数和时钟周期数固定不变

异步控制方式

每条指令或操作按需占用时间。需要使用应答机制。没有时间上的浪费,但是控制复杂

联合控制方式

结合以上两种控制方式。大部分操作序列安排在固定的机器周期中。个别的难以确定的操作则以执行部件的“应答”信号作为操作的结束

Last updated