流水CPU

流水CPU结构

指令部件

指令队列FIFO

执行部件

原理

在流水线(Pipeline)中必须是连续的任务,只有不断提供任务才能充分发挥流水线的效率

把一个任务分解为几个有联系的子任务,每个子任务由一个专门的功能部件实现

流水线中各段时间应尽量相等,否则会引起堵塞、断流现象

流水线需要装入时间和排空时间。流水线完全充满时才能充分发挥效率

指令处理的分解

IF(Instruction Fetch)取指

ID(Instruction Decode)译码

EX(Execution)执行

WB(Write Back)写回

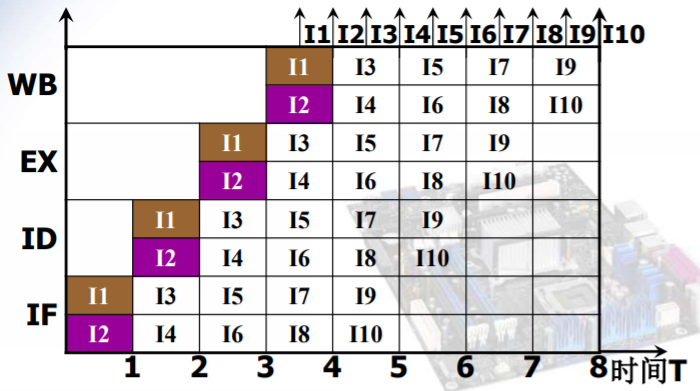

四级指令流水线

时空图

非流水线时空图:

上一条指令与下一条指令存在时间上的重叠,每一个时钟周期就能输出一个结果

超标量流水线时空图:

在标量流水线基础上增加空间并行技术,一次执行多条指令

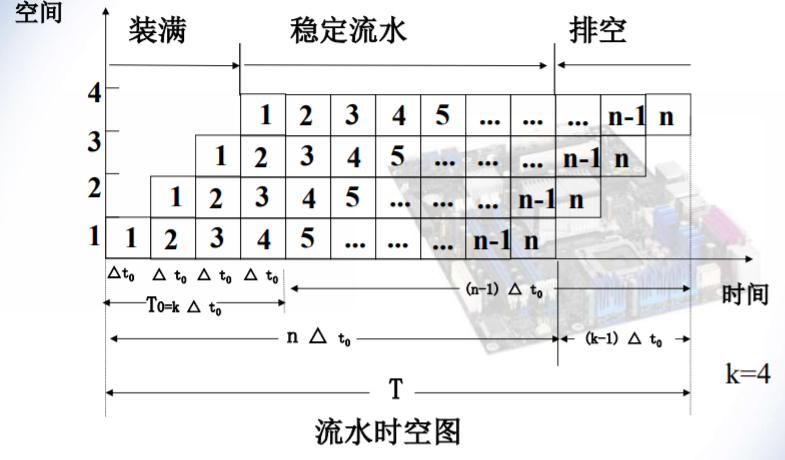

线性流水线有三个阶段:

性能指标

加速比(Speedup Ratio)

衡量不使用流水线和使用流水线完成同样任务所用的时间比

k级流水线时钟周期t,则不使用流水线完成n各任务所需时间T0=nkt,使用k级流水线完成n个连续任务所需时间为Tk=(k+n-1)t

显然当n远大于k时最大加速比为k

吞吐率

单位时间完成的任务数

n为任务数,Tk为完成n各任务的时间,则吞吐率TP = n / Tk

显然n趋近无穷时最大吞吐率为1/t

流水线冲突

资源相关

如流水线的不同部分在同一时钟周期同时访问内存。假设某流水线分为五部分:取指、译码、执行、取存、写回,那么在流水线执行时取指和取存都会访问存储器,这就导致了冲突

解决方案

某条指令在冲突时停顿一拍

分离数据与指令的存储

数据相关

流水线的不同节拍同时需要读写一个地址的数据。如运算结果在第3拍需要写入内存,而后面的操作需要用到这个内存。可能会发生“先读后写”冲突。注意同时读是不冲突的

为了解决冲突,流水CPU设置了许多结果缓存寄存器,保存结果给后面的指令直接使用

控制相关

由转移指令引起。因为流水线不知道判定结果,不知道应该顺序执行还是转移执行。常用处理技术:

延迟转移 - “先执行再转移”。在条件转移之前已经有若干个指令进入流水线了,把这些指令执行完毕,如果正好是目标指令则没有浪费时间

分支预测 - 猜测分支的方向

静态分支预测。硬件固定的预测方式,如总是转移或总是不转移

动态分支预测。内部保存一个表,记录最近的以此转移的情况,然后根据此情况转移

Last updated