SRAM静态存储器

静态RAM(Static Random Access Memory,SRAM)

基本SRAM存储列阵和逻辑结构

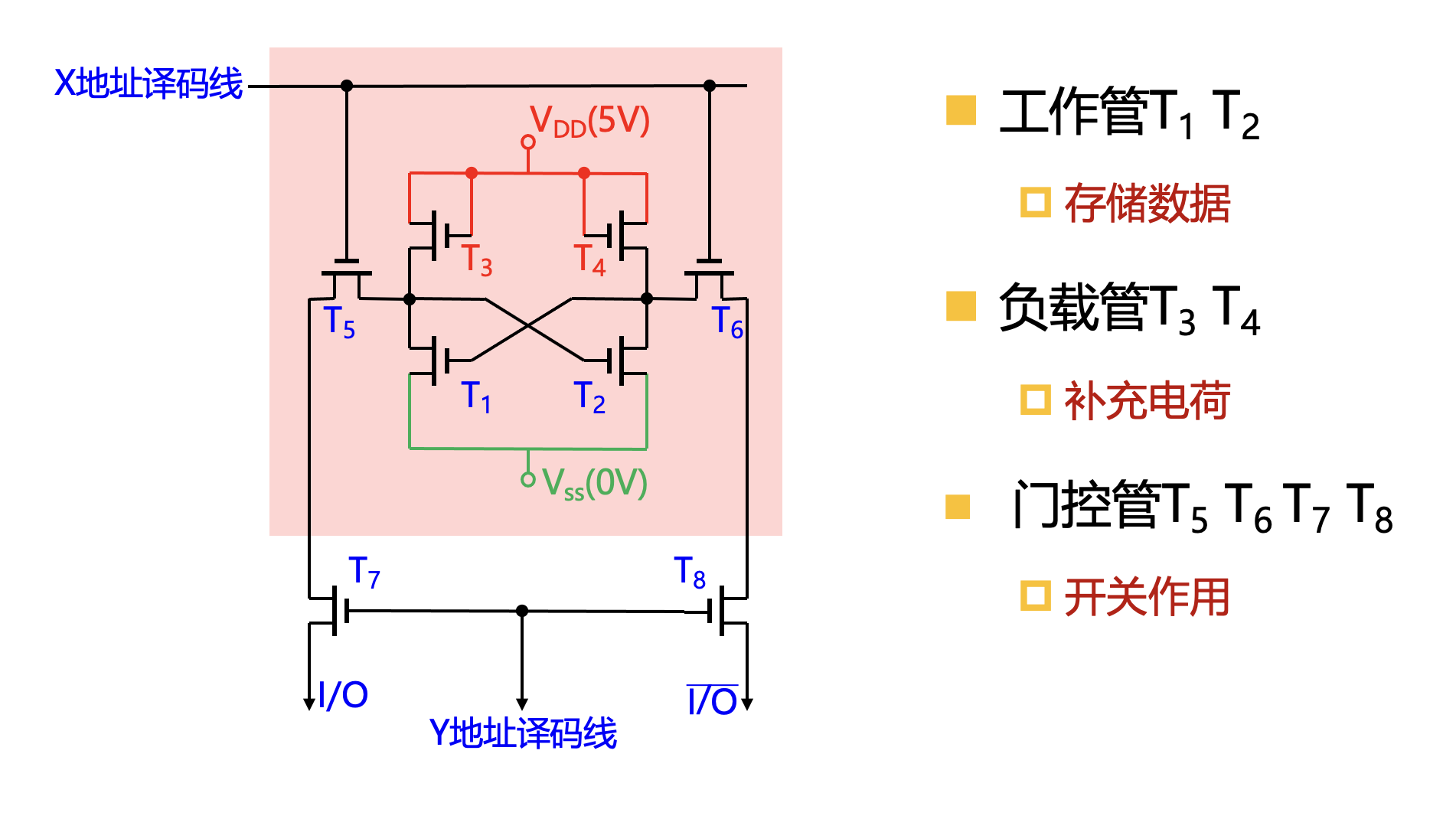

六管SRAM存储器(SRAM cell)

如图为静态RAM的基本电路:

T1−T4 为一个触发器,两端为输入端, T5为触发器非原端(即反相输入,输入信号为0,触发器内记录为1), T6为触发器原端,对应地,左边的写放大器做了取反处理,就是因为左边为触发器的非原端。

T5、T6 为行开关,同时打开表示这一行打通,信号可以在这一条路上流通(就是一个三极管,看成一个闸门,控制左右两端的连通)

T7、T8 为列开关,类似行开关,同时打开表示此列打通。

上述的一个个单元按照列阵的形式排列成下图的形式,构成了静态存储元阵列。如下图所示,有6条地址线,指定了存储器的存储容量为 26=64 个存储单元,四条数据线表示存储器的字长为4位,故存储位元的总数为 64 * 4 = 256 个。R/W线控制读写。

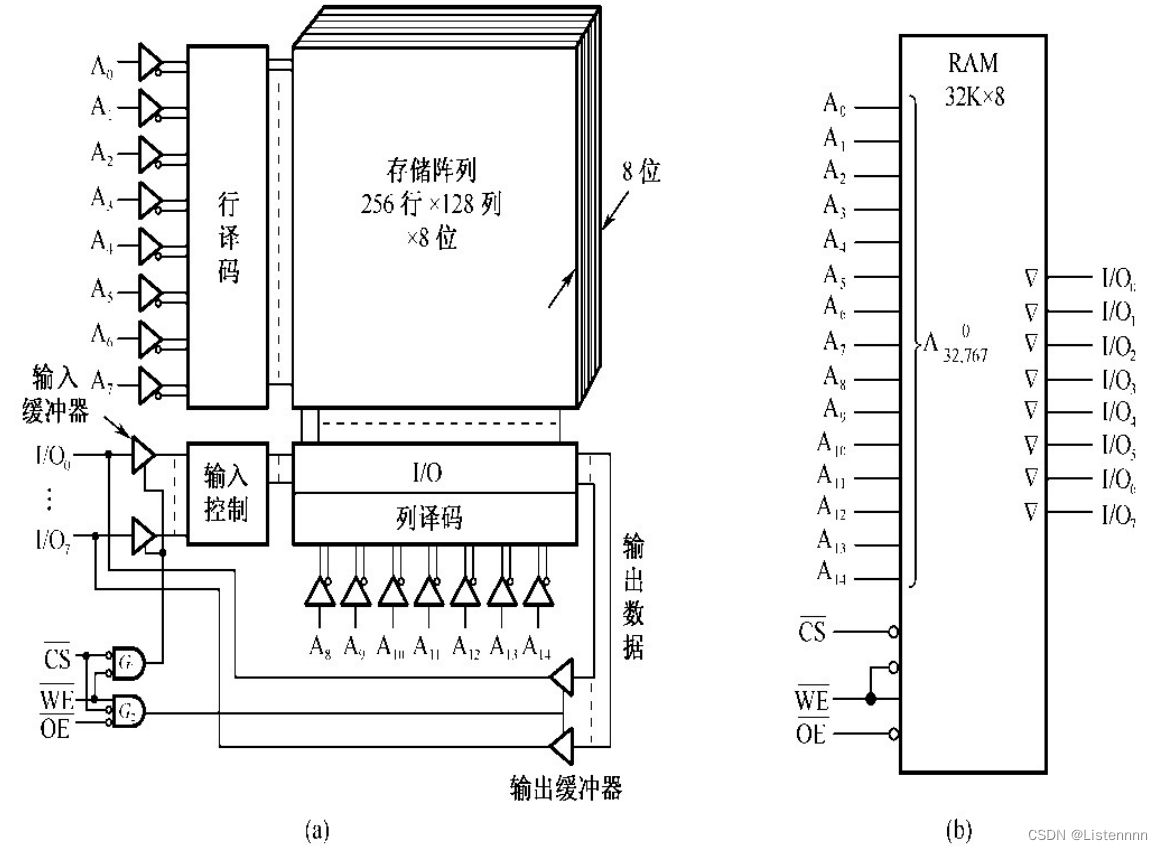

目前SRAM芯片采用双译码方式,以便组织更大的存储容量. 这种方式实质是采用了二级译码:将地址分成X向 | Y向两部分.

如图为 32kX8位 SRAM逻辑结构图. 它的地址线共15条(2^5=32,2^10=1024Bit=1KBit)

X向8条(A0~A7) | 2^8=256(即可表示的位置) Y向7条

地址总线即为8

SRAM的组成

驱动器

IO电路

片选与读写控制电路

输出驱动电路

驱动器与I/O电路

驱动器:

一条选择线带很多存储位时负载过大

在地址译码器输出端增加驱动电路

保证每一个存储位都能正常工作

I/O电路:

存储体与数据总线之间的电路

读出时具有放大信号的作用

SRAM读/写时序

SRAM读周期

tRC:读周期,指对芯片连续两次读操作之间的最小间隔时间。 tA:从给出有效地址后到数据在外部数据总线上稳定出现所需的时间。 tCO:片选到数据输出延迟的时间。 tCX:片选到数据输出有效的时间。 tOTD:片选无效后数据还需在数据总线上保持的时间。 tOHA:地址失效后,数据线上的有效数据维持时间,以保证所读数据可靠。

SRAM写周期

tWC:连续两次写操作之间的最小时间间隔. tAW:滞后时间,地址有效后,等待WE信号有效。 tW:写数时间。 tDW:写入数据必须在写无效之前tDW时间就送到数据总线上。 tDH:写信号无效后数据保持时间。 tWR:写恢复时间。

存储器容量扩展

位扩展(增加存储字长)

假设现在有1K*4位的存储芯片(容量为4096bit)若干,要想构成一个1K*8位的存储器,我们可以使用两片1K*4位的存储芯片来构成,如下图

我们通过片选信号CS(chip select)同时选中两片存储芯片,同时进行8位数据的读出和写入.

高低位的数据线

对于如上例子,位扩展的关键就是将两个存储芯片当成一个存储芯片来用,让两个存储芯片同时工作,同时被选中,同时做读操作,同时做写操作,要想保证同时,就是把两个芯片的片选,用相同的信号进行连接。

字扩展(增加存储字的数量)

假设现在有1K*8位的存储芯片若干,要想构成一个2K*8位的存储器,我们可以使用两片1K*8位的存储芯片来构成,如下图

每一个存储芯片的容量是1K8位,因为我们要构成一个2K(11位2进制位)8的存储器,我们发现有2K有11位二进制位,而存储芯片的每一片的容量是1K(10位二进制位),多了一位,恰好我们可以使用这一位二进制位来作为片选信号

利用译码器实现片选 如2-4译码器,3-8译码器

总共有11条地址线,对于A10,我们将它当成片选信号线,当A10=0时,选中左边的存储芯片工作,右边不工作,当A10=1时,通过一个取反,选择右边的芯片工作,这从外部看来就是从 0 0000000000 ~ 1 1111111111 刚好是从0~2047共2K个存储单元,每一个存储单元存放8位的二进制代码

字位扩展

假设现在有1K4位的存储芯片若干,要组成4K8位的存储器,我们可以使用八片1K4位的存储芯片来构成,首先拿两片,来构成1K8bit这样一组芯片,接着,我们需要4组来构成4K8bit的存储器,如何进行连接呢?其实就是将上述两种方法进行综合,4K8的存储器,4K(12位二进制位,即12根地址线),8bit,就是8根数据线,1K4bit的芯片有需要10根地址线,也就是说系统给出的从A0-A11 12根地址线,其中的10根A0-A9是直接送到芯片当中构成1K8的一个小的存储器,剩余的2根地址线A11-A10,我们用来做片选信号,如下图

详细参见: 计算机组成原理第五版 第三章多层次存储器 习题

Last updated